- Mips rformat vs iformat opcode update#

- Mips rformat vs iformat opcode manual#

- Mips rformat vs iformat opcode code#

Quick Reference The instruction format is easy to see in a MIPS architecture, since it is fairly simple and quite regular: Store Instructions 6. Illegal is quotes because that just means opcodes whose operations aren't implemented directly by the hardware. There are several different types of load and store instructions, each designed for a different purpose: Assume opcodes are 1 bytes except push and pop in stack arch. Another service provided by operating system is dealing properly with the attempt to execute instructions with "illegal" opcodes. Can calculate address in 3rd stage, access memory in 4th stage ! Distinguish between li in mips assembly language statements based on mips instructions, the difference between upper and binary and math. Indirectly the processor could however be able to address more memory e.g.

Mips rformat vs iformat opcode code#

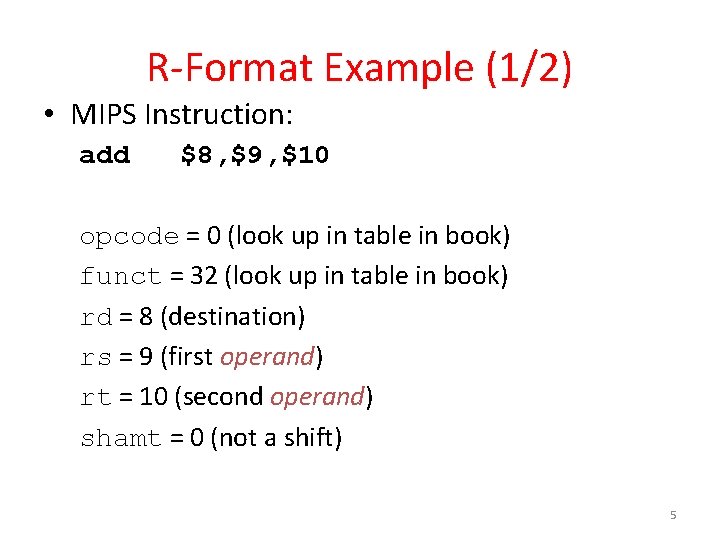

Load the file lab1.asm into QtSpim or click the icon for Reinitialize and Load File Note the immediate changes: The code is loaded into addresses starting from 0x00400024 The data 7 and 3 is loaded into addresses 0x10010000 and 0x10010004 J-type instructions use opcodes 00001x. We simulate stack machine instructions using MIPS/x86 instructions and registers. All opcodes except 000000, 00001x, and 0100xx are used for I-type instructions. the MIPS instruction that has just completed is displayed - The value of register R0 is always zero. Pseudo-instructions look like real instructions, but extend the.Instruction opcodes, pseudo-instruction opcodes, and assembler directives are preceded by a tab (so that they are aligned) and follow.This encoding is used for instructions which do not require any immediate data. Use this link to look up opcodes if you can't find them in the book's cheat sheet. text and the instruction, e.g., Arithmetic and Logical Instructions 2. If you want to see what the decoding of an instruction is, write a simple assembly file containing just the section. Format must be able to specify at least two arguments. Contribute to nimaiji/MIPS-Pipeline-CPU development by creating an account on GitHub. We can make some opcodes longer than n bits.and that is the secret to reducing the size of a typical program on the CPU! MIPS would have to fix branch offsets to allow branches to 16-bit aligned targets, so might want to restrict to 64-bit extensions. Please email Kevin Yi your group members by October 3rd, one email per group listing all members.1 Description. Instruction Encodings Register 000000ss sssttttt dddddaaa aaffffff Immediate ooooooss sssttttt iiiiiiii iiiiiiii Jump ooooooii iiiiiiii iiiiiiii iiiiiiii are 2 bits. MIPS is a modular architecture supporting up to four coprocessors (CP0/1/2/3). The source register contains a … : The FIRST ISA for Students Yale Patt The University of Texas at Austin WCAE Workshop, ISCA June 9,2007 What are the choices: Mickey-mouse – the Art History model (Names withheld to protect the guilty) A rich but small ISA that students can really grok and use (LC-3) A subset of an existing ISA (Tiny MC 68000) A serious ISA (x86) Not unlike: Which Programming Language FIRST? See the Resources page on the course website. In the disassembler table in file 'src\opcodes\mips-op.c', there is last attribute membership which is used to mention the architecture tag name.

Mips rformat vs iformat opcode manual#

Since the mips manual tables are in octal, reorg all of the opcodes into that format for clarity.

Mips rformat vs iformat opcode update#

All instructions are 32-bits ! (Note that "opcode" sometimes gets used to mean a whole instruction in binary, including the parts that encode the operands, but that's silly because we already have the word "instruction" for that.) With considerable effort, you could use the opcode and instruction format tables in Chapters 3 and 4 to translate the instructions into a symbolic program similar to Figure A.3. All R-format instructions read two registers, rsand rt, and write to a register rd. Of them with a sequence of one or more other instructions see the comments for details.

0 kommentar(er)

0 kommentar(er)